Federal Aviation Administration William J. Hughes Technical Center Aviation Research Division Atlantic City International Airport New Jersey 08405

# Assurance of Multicore Processors in Airborne Systems

July 2017

**Final Report**

This document is available to the U.S. public through the National Technical Information Services (NTIS), Springfield, Virginia 22161.

This document is also available from the Federal Aviation Administration William J. Hughes Technical Center at actlibrary.tc.faa.gov.

U.S. Department of Transportation **Federal Aviation Administration**

#### NOTICE

This document is disseminated under the sponsorship of the U.S. Department of Transportation in the interest of information exchange. The U.S. Government assumes no liability for the contents or use thereof. The U.S. Government does not endorse products or manufacturers. Trade or manufacturers' names appear herein solely because they are considered essential to the objective of this report. The findings and conclusions in this report are those of the author(s) and do not necessarily represent the views of the funding agency. This document does not constitute FAA policy. Consult the FAA sponsoring organization listed on the Technical Documentation page as to its use.

This report is available at the Federal Aviation Administration William J. Hughes Technical Center's Full-Text Technical Reports page: actlibrary.tc.faa.gov in Adobe Acrobat portable document format (PDF).

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                |                                                                                                                                                                                                                            | Technical Papert Decumentation Page                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| 1. Report No.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2. Government Accession No     | ).                                                                                                                                                                                                                         | Technical Report Documentation Page<br>3. Recipient's Catalog No. |

| DOT/FAA/TC-16/51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                |                                                                                                                                                                                                                            |                                                                   |

| 4. Title and Subtitle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                |                                                                                                                                                                                                                            | 5. Report Date                                                    |

| ASSURANCE OF MULTICORE PROCESSORS IN AIRBORNE SYSTEMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                |                                                                                                                                                                                                                            | July 2017                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                |                                                                                                                                                                                                                            | 6. Performing Organization Code                                   |

| 7. Author(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                |                                                                                                                                                                                                                            | 220410<br>8. Performing Organization Report No.                   |

| Laurence H. Mutuel, Xavier Jean, Vincer<br>Thomas Megel, E. Alepins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | nt Brindejonc, Anthony         | Roger,                                                                                                                                                                                                                     |                                                                   |

| 9. Performing Organization Name and Address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                |                                                                                                                                                                                                                            | 10. Work Unit No. (TRAIS)                                         |

| Thales Avionics, Inc.<br>2733 S Crystal Drive, suite 1200                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                |                                                                                                                                                                                                                            | 11. Contract or Grant No.                                         |

| Arlington, VA 22202                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                |                                                                                                                                                                                                                            |                                                                   |

| 12. Sponsoring Agency Name and Address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                |                                                                                                                                                                                                                            | 13. Type of Report and Period Covered                             |

| Federal Aviation Administration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                |                                                                                                                                                                                                                            | Final Report, 11/10/14 – 11/08/2016                               |

| William J. Hughes Technical Center                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                |                                                                                                                                                                                                                            | 14. Sponsoring Agency Code                                        |

| Aviation Research Division                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                |                                                                                                                                                                                                                            | AIR-134                                                           |

| Atlantic City International Airport, NJ 08<br>15. Supplementary Notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 405                            |                                                                                                                                                                                                                            |                                                                   |

| The FAA William J. Hughes Technical C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | enter Aviation Researc         | h Division Technical I                                                                                                                                                                                                     | Monitor was Srini Mandalapu.                                      |

| 16. Abstract This report documents the issues related to software assurance applied to multicore processors (MCPs) and the safety implications pertaining to the use of MCPs in flight-critical applications. In recent years, the use of MCPs in avionics has supported the increase in performance and level of integration of safety-critical functions. However, MCPs stretch the current hardware and software assurance processes. As MCPs were not initially designed for aircraft applications, a preemptive investigation of the potential safety concerns is warranted. The main concern regarding the use of MCPs in the safety-critical aerospace domain is their lack of predictability. Therefore, their use must be integrated into a systems approach wherein the need for determinism is considered for each function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                |                                                                                                                                                                                                                            |                                                                   |

| implemented on the MCP. This statement justifies the use of a top-down safety method as the primary approach to be applied t<br>all failure conditions, including those specific to MCPs. The outcome is a set of qualitative and quantitative safety requirements<br>and the allocation of development assurance level (DAL) to each software application according to the identified criticality level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                |                                                                                                                                                                                                                            |                                                                   |

| The proposed approach to interference analysis in the context of safety processes is close to partitioning analyses. It is composed of two complementary analyses: a top-down analysis followed by a bottom-up analysis. The top-down analysis allows for isolating high-level sources of non-determinism affected by the function/task allocation to cores, the software scheduling strategy, and the selection of MCPs based on usage domain (UD). This consideration of UD is used to orient and bound the complementary bottom-up analysis. Finally, the top-down analysis prepares for the determination of mitigation strategies for the sources of non-determinism that remain in the UD. The bottom-up analysis is conventional from a safety standpoint. The key point is that the complexity of MCPs no longer allows for claims of exhaustiveness unless the top-down analysis is performed beforehand to bind its scope. The interference-aware safety analysis consists of three sequential steps: the identification of an interference path; performance of an interference mitigation. The last step is to implement mitigation for interference channels identified as bounded but unacceptable, unbounded, and faulty. The mitigations can be internal or external to the processor. This report details each of the steps of the proposed safety analyses. |                                |                                                                                                                                                                                                                            |                                                                   |

| The limitations in existing guidance can be mitigated by the implementation of the proposed complementary top-down and bottom-up analyses. This approach is close to that for integrated modular avionics and is, therefore, dedicated to complex computational systems with high integration levels. It is perfectly adapted to MCP concerns.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                |                                                                                                                                                                                                                            |                                                                   |

| 17. Key Words                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                | 18. Distribution Statement<br>This document is a                                                                                                                                                                           | available to the U.S. public through the                          |

| Multicore processors, Software assur<br>determinism, Interference, Failure, Us<br>method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | age domain, Safety             | National Technical Information Service (NTIS), Springfield,<br>Virginia 22161. This document is also available from the<br>Federal Aviation Administration William J. Hughes Technical<br>Center at actlibrary.tc.faa.gov. |                                                                   |

| 10. Security Classif (of this report)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 20 Security Classif (of this p | 2000)                                                                                                                                                                                                                      | 04 Na of Dance 00 Drive                                           |

|                                        | Center at activitary.u               | c.laa.gov.       |           |

|----------------------------------------|--------------------------------------|------------------|-----------|

| 19. Security Classif. (of this report) | 20. Security Classif. (of this page) | 21. No. of Pages | 22. Price |

| Unclassified                           | Unclassified                         | 121              |           |

|                                        |                                      |                  |           |

# ACKNOWLEDGEMENTS

This research has been coordinated with the technical experts and reviewers at Thales Avionics SAS by Cyril Marchand. Didier Regis, Marc Fumey, Helene Misson, and Guy Berthon acted as internal reviewers for this report.

# TABLE OF CONTENTS

| EXEC | CUTIVE       | E SUMMARY                                                                                                                                                       | xi                   |

|------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 1.   | INTR         | CODUCTION                                                                                                                                                       | 1                    |

|      | 1.1<br>1.2   | Background<br>Purpose                                                                                                                                           | 1<br>1               |

| 2.   | APPR         | ROACH                                                                                                                                                           | 3                    |

|      | 2.1          | Generic Safety Process                                                                                                                                          | 3                    |

|      |              | <ul><li>2.1.1 Top-down Methods for Safe Design Process</li><li>2.1.2 Bottom-up Methods for Safety Verification Process</li></ul>                                | 4<br>4               |

|      | 2.2<br>2.3   | Dissociating Real-time Constraints from Safety Constraints<br>Interference-aware Safety Process                                                                 | 4<br>6               |

|      |              | <ul><li>2.3.1 Approach</li><li>2.3.2 Steps to be Performed</li></ul>                                                                                            | 8<br>10              |

| 3.   | COM          | PUTER ARCHITECTURES                                                                                                                                             | 12                   |

|      | 3.1<br>3.2   | Federated and Integrated Avionics Architectures<br>Classification Criteria                                                                                      | 12<br>13             |

|      |              | <ul><li>3.2.1 Computing Performance</li><li>3.2.2 Constraints of Real-time</li><li>3.2.3 Safety Considerations</li><li>3.2.4 Certification Frameworks</li></ul> | 13<br>13<br>14<br>14 |

|      | 3.3          | Summary of Key Features for Comparing Architectures                                                                                                             | 15                   |

| 4.   | ISSU<br>PROC | ES WITH CURRENT GUIDANCE FOR MCP DEVELOPMENT<br>CESS                                                                                                            | 16                   |

|      | 4.1<br>4.2   | Verification Guidance and CAST Position Paper #32<br>Current Guidance with Respect to Interferences                                                             | 16<br>18             |

|      |              | <ul><li>4.2.1 Revised FAA Issue Paper on MCP</li><li>4.2.2 EASA Certification Memorandum SWCEH-001</li><li>4.2.3 RTCA DO-297</li></ul>                          | 18<br>18<br>19       |

| 5.   | MCP          | FAILURE MODES AND HAZARD IDENTIFICATION                                                                                                                         | 19                   |

|    | 5.1<br>5.2               | MCP Description<br>Description of Failure Modes                                                                                                                                                               | 19<br>20             |

|----|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

|    |                          | <ul><li>5.2.1 Types of Failures</li><li>5.2.2 Expression of Failure Modes at Logical Level</li><li>5.2.3 Failure Modes at Hardware-Software Interface</li></ul>                                               | 20<br>21<br>23       |

|    | 5.3                      | Allocation of Hazards onto MCP Architecture                                                                                                                                                                   | 24                   |

|    |                          | <ul><li>5.3.1 Hazards Associated with the OS/Hypervisor</li><li>5.3.2 Hazards Associated with the Interconnect</li><li>5.3.3 Core Failures</li></ul>                                                          | 24<br>24<br>25       |

|    | 5.4                      | Identification of Interference Paths                                                                                                                                                                          | 25                   |

|    |                          | <ul><li>5.4.1 Bottom-up Analysis to Identify Interferences Sources</li><li>5.4.2 Top-Down Analysis for Identification of Interference Paths</li></ul>                                                         | 26<br>27             |

|    | 5.5                      | Primary Causal Factors for Unreliable Hardware Operation                                                                                                                                                      | 28                   |

| 6. | DETE                     | ERMINATION OF EFFECTS                                                                                                                                                                                         | 28                   |

|    | 6.1                      | Safety Impacts of Non-determinism                                                                                                                                                                             | 28                   |

|    |                          | <ul><li>6.1.1 Top-down Analysis in MCP Design</li><li>6.1.2 Bottom-up Analysis in MCP Design</li></ul>                                                                                                        | 28<br>34             |

|    | 6.2                      | Classification of Impact for Interferences                                                                                                                                                                    | 45                   |

|    |                          | <ul><li>6.2.1 Objectives and Results of the Interference Analysis</li><li>6.2.2 Example of Interference Impact on Software</li></ul>                                                                          | 46<br>47             |

|    | 6.3                      | Effects of Interconnect Failures                                                                                                                                                                              | 49                   |

| 7. | MITI                     | GATION MEANS                                                                                                                                                                                                  | 50                   |

|    | 7.1<br>7.2<br>7.3<br>7.4 | Mitigation Techniques by MCP Features<br>Online Error Detection, Recovery, and Repair Schemes<br>Mitigations of Interferences<br>Fault Detection, Isolation, and Reconfiguration for Fail-Operational Systems | 50<br>51<br>53<br>54 |

| 8. | SELE                     | CTED EXAMPLES                                                                                                                                                                                                 | 55                   |

|    | 8.1                      | Methods for Interference Analysis                                                                                                                                                                             | 55                   |

|    |                          | <ul><li>8.1.1 Analysis of Processors Containing Black-Box Components</li><li>8.1.2 Methods for Global Interference Penalties</li></ul>                                                                        | 55<br>59             |

|     |            | 8.1.3   | Local Analyses                                           | 60 |

|-----|------------|---------|----------------------------------------------------------|----|

|     | 8.2        | Examp   | ples of Internal Mitigations For Interference            | 62 |

|     |            | 8.2.1   | Interference Reduction Techniques                        | 64 |

|     |            | 8.2.2   | Bounded Interference Solutions                           | 66 |

|     |            | 8.2.3   | Interference-Free Solutions                              | 68 |

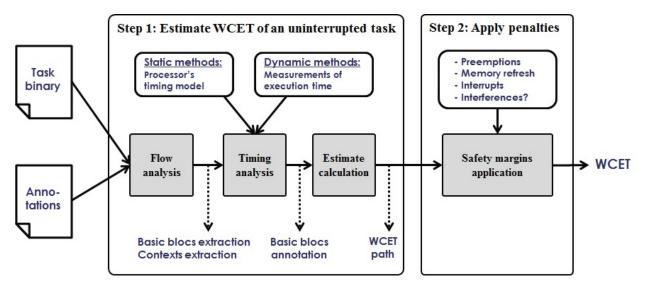

|     | 8.3        | Mitiga  | ation of Variable Execution Time by WCET Techniques      | 71 |

|     |            | 8.3.1   | At System Level                                          | 71 |

|     |            | 8.3.2   | At Electronic Devices Level                              | 71 |

|     |            | 8.3.3   | At Microprocessor Level                                  | 72 |

|     | 8.4        | -       | ation of Single Event in MCP Scoreboard                  | 72 |

|     | 8.5        |         | tolerance in Network-on-Chip Systems                     | 73 |

|     | 8.6        |         | e Replication for Fault-tolerant Scheduling              | 73 |

|     | 8.7        | Mitiga  | ation Techniques at Core Level                           | 73 |

|     |            | 8.7.1   | Self-test                                                | 73 |

|     |            | 8.7.2   | Architectural Mitigation                                 | 74 |

|     | 8.8        | Fail-sa | afe and Fail-operational Designs in Automotive Industry  | 74 |

|     | 8.9        | Pair ar | nd Swap Technique for Processor's Degraded Mode          | 75 |

| 9.  | RECO       | OMMEN   | <b>JDATIONS</b>                                          | 75 |

|     | 9.1        | Identif | fied Gaps In Existing Guidance                           | 75 |

|     |            | 9.1.1   | Context of Determinism                                   | 75 |

|     |            | 9.1.2   | Limitations of Conventional Assurance Approach           | 75 |

|     | 9.2        | Recon   | nmended Approach                                         | 76 |

|     |            | 9.2.1   | Recommended Activities                                   | 76 |

|     |            | 9.2.2   | Pros and Cons of Conventional and Recommended Approaches | 78 |

|     |            | 9.2.3   | Definition of MCP Stakeholders and Associated Activities | 78 |

|     | 9.3        | Criteri | a for Determinism                                        | 82 |

|     |            | 9.3.1   | Criteria Associated With Top-down Approach               | 82 |

|     |            | 9.3.2   | Criteria Associated With Bottom-up Approach              | 83 |

| 10. | CON        | CLUSIC  | DNS                                                      | 84 |

| 11. | REFERENCES |         | 86                                                       |    |

9.

APPENDICES

A—GLOSSARY B—WORST CASE EXECUTION TIME EVALUATION ASPECTS C—ACTIVITIES AND DATA RECOMMENDED TO BE PRODUCED FOR COTS ASSURANCE

# LIST OF FIGURES

| Figure |                                                                                 | Page |

|--------|---------------------------------------------------------------------------------|------|

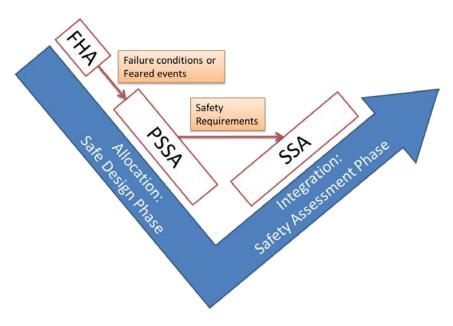

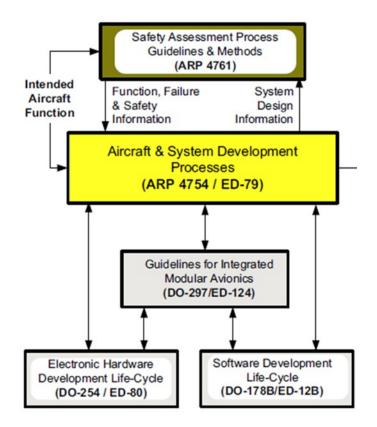

| 1      | Overview of generic safety process                                              | 3    |

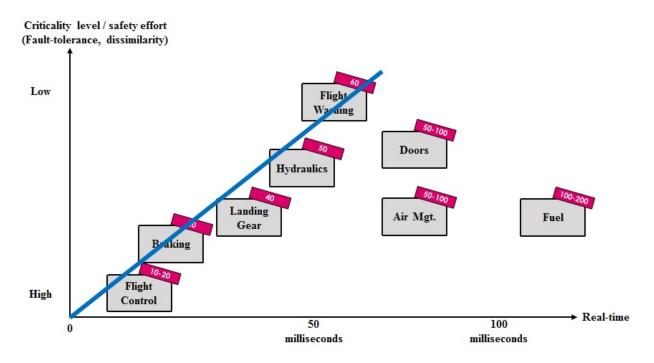

| 2      | Correspondence between criticality level and real-time constraint               | 6    |

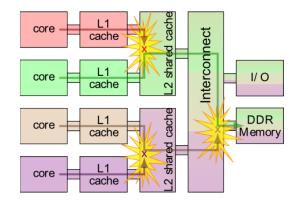

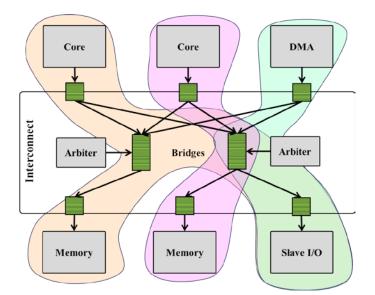

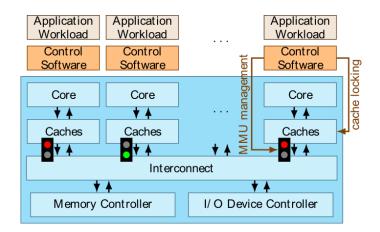

| 3      | Interferences due to concurrent access on shared resources                      | 7    |

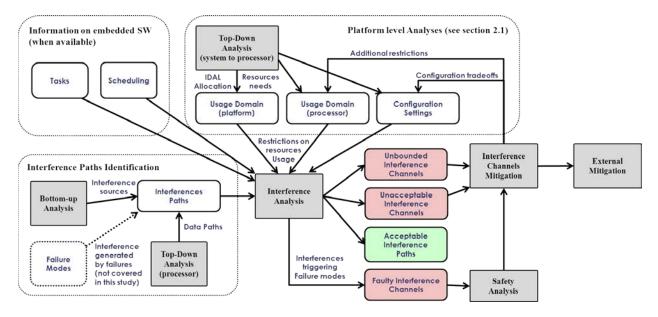

| 4      | Overview of the proposed interference-aware safety process                      | 8    |

| 5      | Certification frameworks                                                        | 15   |

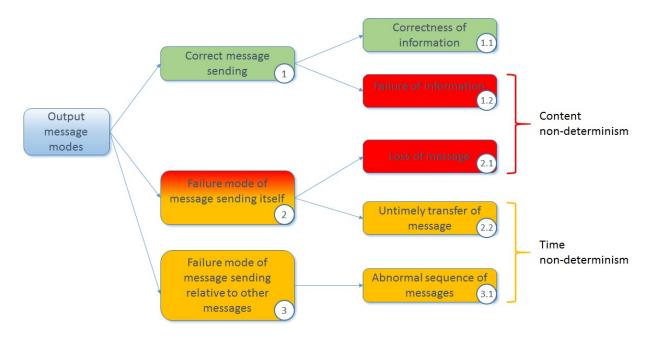

| 6      | Relationship between failure mode classification and non-determinism modes      | 22   |

| 7      | Example of interference path                                                    | 26   |

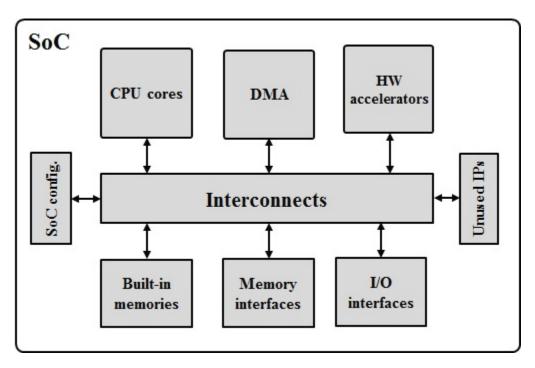

| 8      | MCP meta-model                                                                  | 34   |

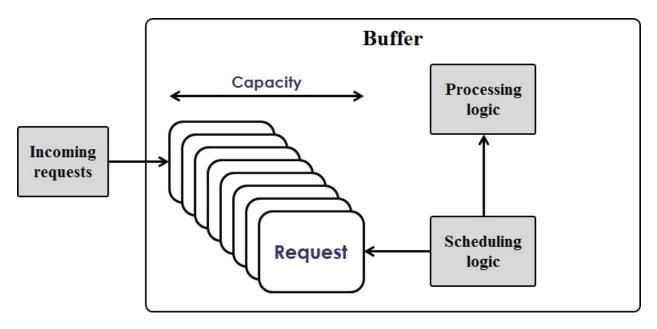

| 9      | Buffer structure                                                                | 38   |

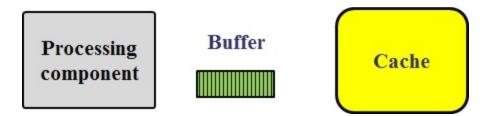

| 10     | Graphical convention                                                            | 40   |

| 11     | Example of memory hierarchy                                                     | 40   |

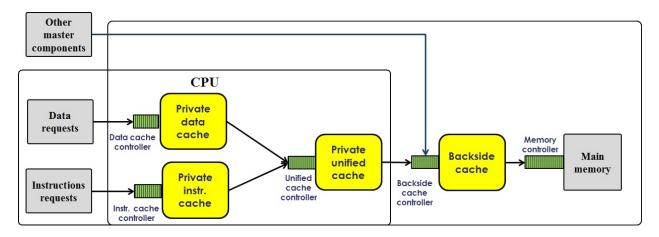

| 12     | Overview of DRAM controller                                                     | 41   |

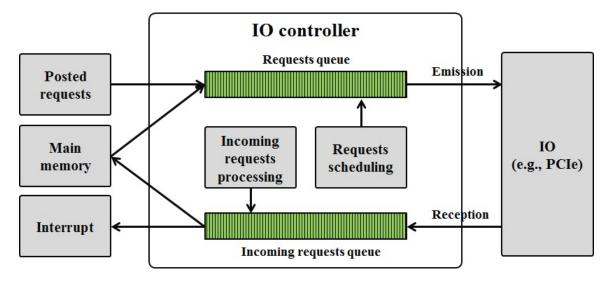

| 13     | Overview of I/O interface                                                       | 43   |

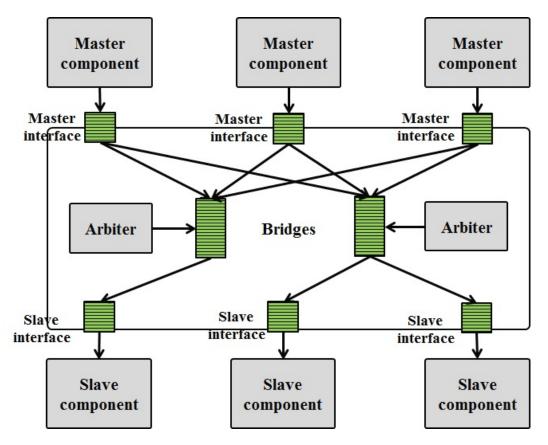

| 14     | Overview of interconnect                                                        | 44   |

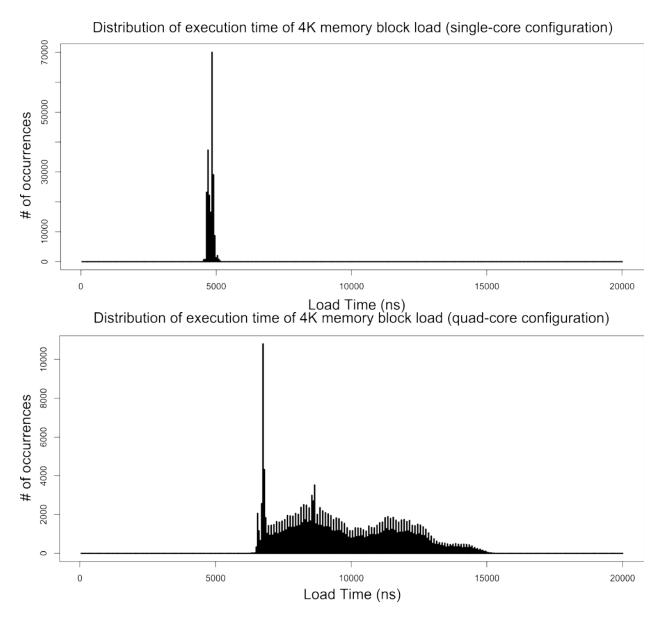

| 15     | Example of impact of interferences on 4K memory load operations (1 vs. 4 cores) | 48   |

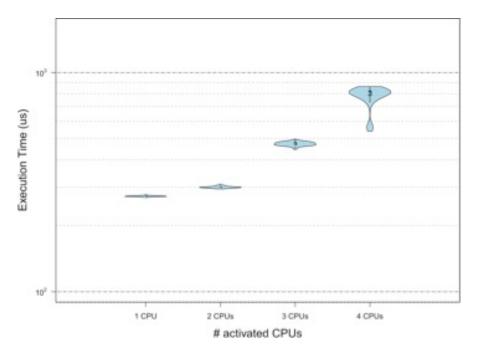

| 16     | Impact of interferences on a piece of application vs. number of active cores    | 49   |

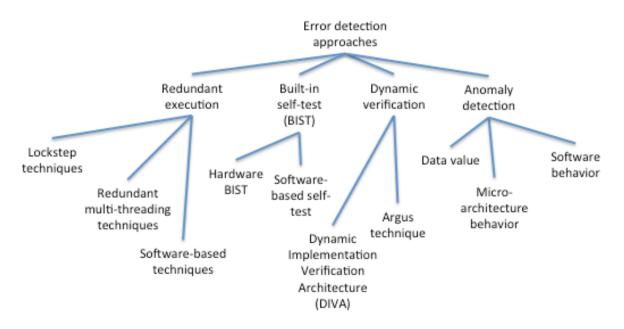

| 17     | Topology of online error detection techniques [25]                              | 52   |

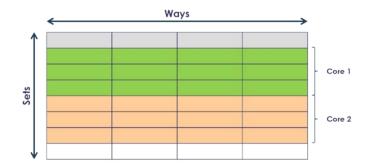

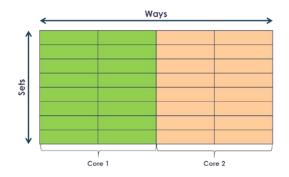

| 18     | Example of colored cache shared between two cores                               | 65   |

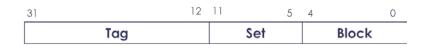

| 19     | Address sections from the cache's point of view                                 | 65   |

| 20     | Illustration of cache partitioning                                              | 65   |

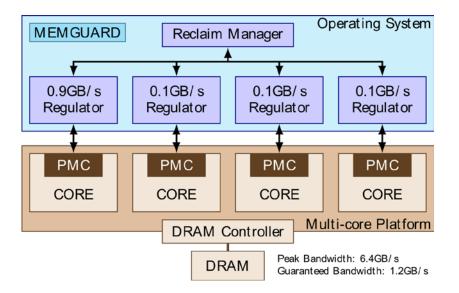

| 21     | Overview of MemGuard mechanism                                                  | 67   |

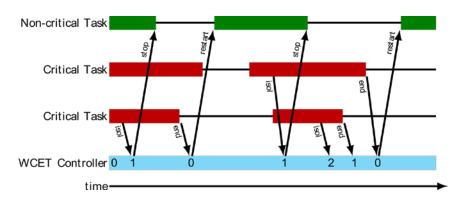

| 22     | Overview of distributed WCET controller                                         | 68   |

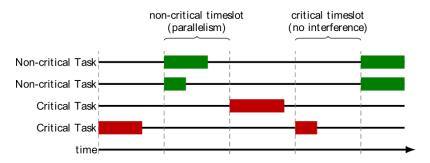

| 23     | Example of interference-free schedule                                           | 69   |

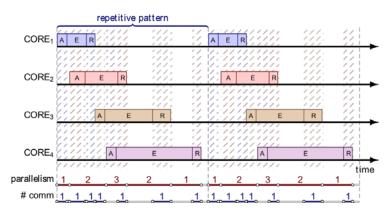

| 24     | Example of deterministic execution model schedule [62]                          | 69   |

| 25     | Overview of Marthy control software                                             | 71   |

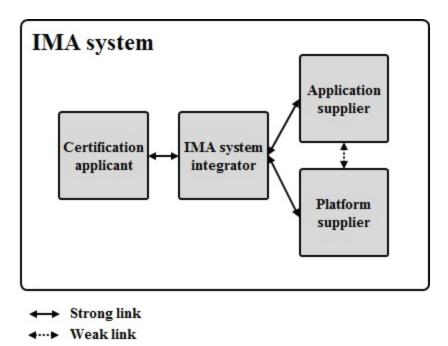

| 26     | Relationship between stakeholders of MCP integration in bottom-up scheme        | 79   |

# LIST OF TABLES

| Table |                                                                                    | Page |

|-------|------------------------------------------------------------------------------------|------|

| 1     | Key features of high-performance IMA and federated avionics architectures          | 16   |

| 2     | Sources of timing non-determinism for cache paradigm                               | 37   |

| 3     | Sources of timing non-determinism for buffer paradigm                              | 39   |

| 4     | Mitigation means for MCP features                                                  | 51   |

| 5     | Example of interference channel numbering                                          | 57   |

| 6     | Surveys of interference mitigation techniques                                      | 62   |

| 7     | Classes of interference mitigation techniques and targeted interference channels   | 63   |

| 8     | Proposed level of bottom-up studies determined by real-time and safety constraints | 77   |

| 9     | Summary of possible approaches for coverage of non-determinism in MCP              | 78   |

| 10    | Activities of IMA stakeholders                                                     | 80   |

| 11    | Summary of activities for MCP stakeholders                                         | 81   |

# LIST OF ABBREVATIONS AND ACRONYMS

| AEH   | Airborne electronic hardware                                    |

|-------|-----------------------------------------------------------------|

| AMP   |                                                                 |

| API   | Asymmetrical multiprocessing                                    |

|       | Application program interface                                   |

| ARP   | Aerospace Recommended Practices                                 |

| ASIL  | Automotive Safety Integrity Level                               |

| BIST  | Built-in self-test                                              |

| CASP  | Concurrent Autonomous chip self-test using stored test patterns |

| CFG   | Control flow graph                                              |

| CM    | Certification Memorandum                                        |

| COTS  | Commercial off-the-shelf                                        |

| CPU   | Core processing unit                                            |

| DAL   | Development Assurance Level                                     |

| DDR   | Double data rate                                                |

| DMA   | Direct memory access                                            |

| DRAM  | Dynamic random access memory                                    |

| EASA  | European Aviation Safety Agency                                 |

| ECC   | Error-correcting code                                           |

| FDAL  | Functional development assurance level                          |

| FHA   | Functional hazard assessment                                    |

| FMEA  | Failure modes and effects analysis                              |

| I/O   | Input/output                                                    |

| IDAL  | Item development assurance level                                |

| IMA   | Integrated modular avionics                                     |

| IOMMU | Input/output memory management unit                             |

| IP    | Intellectual property                                           |

| LRU   | Least recently used                                             |

| MCP   | Multicore processor                                             |

| MMU   | Memory management unit                                          |

| NoC   | Network-on-Chip                                                 |

| OS    | Operating system                                                |

| PCIe  | Peripheral Component Interconnect Express                       |

| PLRU  | Pseudo least recently used                                      |

| PSSA  | Preliminary system safety assessment                            |

| QoS   | Quality of service                                              |

| RTCA  | Radio Technical Commission for Aeronautics                      |

| RTOS  | Real-time operating system                                      |

| SCP   | Single-core processor                                           |

| SEU   | Single-event upset                                              |

| SMP   | Symmetrical multiprocessing                                     |

| SoC   | System-on-Chip                                                  |

| SRAM  | Static random access memory                                     |

| SWAT  | SoftWare Anomaly Treatment                                      |

| TDMA  | Time division multiple access                                   |

| UD    | Usage domain                                                    |

| WCET  | Worst case execution time                                       |

|       |                                                                 |

#### EXECUTIVE SUMMARY

This report documents the issues related to software assurance applied to multicore processors (MCPs) and the safety implications pertaining to the use of MCPs in flight-critical applications.

Most safety-critical avionics systems are defined as "hard real-time," meaning that they must perform their function within predefined deadlines. In some cases, missing a single deadline at system level is considered a failure condition as per Title 14 of the Code of Federal Regulations subpart 1309, for which severity may be classified as catastrophic. The fail-safe principle requires this single hazard to be appropriately mitigated.

On the other hand, the increase in the integration level of safety-critical avionics functions and the need for increased computational performance induce a more widespread use of MCPs. Thanks to these MCPs, avionics computers can host more and more safety-critical functions. The capabilities of MCPs stretch the current assurance processes for both software and hardware. As these processors were not initially designed with aircraft applications in mind, a preemptive investigation of the potential safety concerns is warranted. The main concern related to the use of commercial off-the-shelf MCPs in the aerospace safety-critical domain is their lack of predictability. Therefore, the use of MCPs must be integrated into a systems approach wherein the need for determinism is considered for each function implemented on the MCP. This statement justifies the use of a top-down safety method as the primary approach. In addition to classical safety analysis on mono-core processors, special attention is required when MCPs are used, as some of the additional features of the MCPs could cause specific failure modes.

In the safe design process, top-down safety analysis techniques—such as functional hazard assessment and preliminary system safety assessment—are applied to all failure conditions, including those specific to MCPs. The outcome is a set of qualitative and quantitative safety requirements and the allocation of development assurance levels (DAL) to each software application according to the identified criticality level. This conventional process supports the justification for implementing different functions on an MCP. Consideration of the DAL refinement process allows for dissociating real-time constraints from safety constraints, so that both aspects should be analyzed in parallel but separately as two independent sets of constraints. In addition, the classification of sources of non-determinism into cache type sources, buffer type sources, and interference sources provides a structure to investigate non-determinism in MCPs.

Interferences are hazards specific to MCPs. From the component manufacturer's viewpoint, interference is not a dysfunctional behavior but a performance bottleneck; for the avionics manufacturer, however, interferences are considered dysfunctional behavior. Therefore, the failure modes related to interferences and their effects in terms of loss of integrity, loss of availability, or non-deterministic behavior of embedded applications must be identified and may require mitigation by design.

The proposed approach to interference analysis in the context of safety processes is close to partitioning analyses. It is composed of two complementary analyses: a top-down analysis followed by a bottom-up analysis. The top-down analysis allows for isolating high-level sources of non-determinism affected by the function/task allocation to cores, software scheduling

strategy, and selection of MCPs based on usage domain (UD). This consideration of UD is used to orient and bound the complementary bottom-up analysis.

Finally, the top-down analysis prepares for the determination of mitigation strategies for the sources of non-determinism that remain in the UD. The bottom-up analysis is conventional from a safety standpoint. The key point is that the complexity of MCPs no longer allows for claims of exhaustiveness, unless the top-down analysis is performed beforehand to bind its scope.

The interference-aware safety analysis consists of three sequential steps: the identification of an interference path; performance of an interference analysis to tag each interference channel as acceptable, unacceptable, unbounded, or faulty; and determination of interference mitigation. The identification of interference paths is constrained by the presence of black-box components within the processor. For increased confidence in the result of this step, it is recommended to pair the bottom-up identification with a top-down analysis that evaluates which components are used when embedded software triggers operations to shared resources (unused paths do not need to be further covered). For interference paths on which interferences are actually observed (i.e., an interference channel), the interference analysis will identify if the interference channel has a bounded impact compatible or not with the set interference penalty. If the interference penalty cannot be assessed (unbounded channel), the impact of the interference channel on the software execution time is not properly known; thus, mitigation is required. Finally, if the interference channel triggers a failure mode within the processor (faulty channel), a formalized safety analysis must be conducted with the MCP manufacturer. The last step is to implement mitigation for interference channels identified as bounded but unacceptable, unbounded, and faulty. The mitigations can be internal or external to the processor. Internal mitigations are restrictions set on the MCP, while external mitigations deal with monitoring aspects and sanction strategy.

The interference-aware safety process is to be instantiated on a case-by-case basis based on the equipment, the criticality, and the selected MCP and its internal components' level of detail. Acceptability criteria should be proposed as early as possible in the safe design phase and discussed with the MCP manufacturer.

This report details each of the steps of the proposed safety analyses. A generic fault model for MCP-related non-determinism is developed, including the identification of sources for content and timing non-determinism, and used to illustrate the implementation of the approach. The proposed interference-aware safety analysis is detailed, including the definition of sources of interferences both at physical and logical levels, the determination of safety impacts, and their classification. Mitigation means are classified in terms of error detection, recovery and repair schemes for hardware faults, and design errors. For interference, internal mitigations are surveyed to include interference reduction, bounding, or elimination. Worst-case execution time techniques are also specifically called out as an example of the application of the proposed safety analysis process.

The limitations in existing guidance can be mitigated by the implementation of the proposed complementary top-down and bottom-up analyses. This approach is close to the approach developed for integrated modular avionics and is therefore dedicated to complex computational systems with high integration levels. It is perfectly adapted to MCP concerns.

#### 1. INTRODUCTION

#### 1.1 BACKGROUND

For a multitude of domains, safety-related or not, the user demand for significantly increased performance in reinforced size, weight, and power-constrained environments results in an increased share of multicore processors (MCPs) in the current market segment of highly complex semiconductor devices. On the other hand, legacy embedded avionics systems are based on single-core processors (SCPs) and may suffer from an obsolescence of these components.

Aircraft software applications themselves expand in capabilities that require increased computational performance (e.g., advanced signal processing, manipulation of large quantities of stored information) while achieving gains in size and power (e.g., integrated modular avionics [IMA]). MCPs address this need, so that their usage is foreseen to steadily increase. MCPs are currently used in airborne electronic hardware (AEH), although the technology is conservatively targeting MCPs with no more than two cores.

The capabilities of MCPs stretch the current assurance processes for both software and hardware. The supporting design and verification tools may not be adapted either. Because these processors were not initially designed with aircraft applications in mind, a preemptive investigation of the potential safety concerns is warranted. If the MCP technology driven by the overall market shows a faster growth than the aerospace market is able to address assurance concerns, the potential for a longstanding catch-up situation is possible. The investigation therefore needs to be not only preemptive but also predictive.

One specific safety-related concern is associated with the demonstration of deterministic behavior. The need for determinism is requested at aircraft level and depends on the aircraft function considered. These functions may develop several types of dysfunctional behaviors potentially linked to non-determinism issues.

#### 1.2 PURPOSE

This report informs on the issues related to software assurance applied to MCPs and the safety implications of the use of MCPs in flight-critical applications.

Safety issues associated with the use of MCPs in flight-critical applications are associated with non-determinism. The link between dysfunctional behaviors visible to the users and non-determinism is investigated from both a safety and real-time standpoint. This report proposes to implement safety analyses with specific activities to identify MCP failure modes, assess the severity of their associated failure conditions, analyze the architecture for mitigation of these failure conditions, and determine the effectiveness of the mitigations implemented.

Section 2 describes the proposed approach which includes a top-down and a bottom-up analyses on the design. Furthermore, the potential for modulation of the effort is dependent on the distinction between real-time constraints and safety constraints. Lastly, a specific instantiation is detailed for the proposed safety process applied to the most relevant cause of non-determinism within multicore processors: interferences.

Section 3 gives an overview of two architectures that represent both ends of the spectrum in avionics. Examples from both federated and integrated avionics architectures are used throughout this report.

Section 4 summarizes the existence guidance on MCPs. The identified gaps are addressed in the recommendation section.

Section 5 represents the first step of the safe design process. It discusses MCP failure modes, their description, and their allocation to the MCP architectural features. Specific attention is provided to interferences as the primary cause of non-determinism in MCP.

Section 6 represents the second step of the safe design process. It discusses the safety impacts of non-determinism and proposes a classification of these impacts for the investigation of interferences.

Section 7 represents the third and last step of the safe design process. It discusses the methods and techniques used to mitigate the impacts of MCP failures.

Section 8 collects specific examples where the proposed methods can be implemented. In particular, the performance of an interference analysis is explained in greater details. Worst-case execution time techniques are also detailed as they are commonly used to show mitigation of timing issues.

Section 9 collects recommendations extracted from the findings in sections 2–8. The proposed safety approach is justified from the gaps in existing guidance and the limitation of conventional assurance approaches. Activities supporting the performance of the recommended approach are defined and allocated to the MCP stakeholders. Finally, criteria are defined for each step of the proposed approach so that the achievement of determinism can be demonstrated.

Section 10 contains the references used in this report.

Appendix A is the glossary of terms, while Appendix B provides additional details on worst-case execution time techniques. Appendix C details activities and recommended justification data to be produced for commercial off-the-shelf (COTS) MCP assurance.

#### 2. APPROACH

Most safety-critical avionics systems are defined as hard real-time, that is, they must perform their function within predefined deadlines. In some cases, missing a single deadline at system level is considered a failure condition (see Title 14 Code of Federal Regulations Part 2X.1309) that may be classified as catastrophic. The fail-safe principle requires this single hazard to be appropriately mitigated.

The increase in the integration level of safety-critical avionics functions induces a more widespread use of MCPs. As a consequence, avionics computers can host more and more safety-critical functions and are subjected to real-time constraints according to the criticality of these embedded functions.

The main concern related to the use of COTS MCPs, in the safety-critical domain, is their lack of predictability. The use of MCPs must be integrated in a systems approach wherein the need for determinism is considered for each function implemented on the MCP. This statement justifies the use of a top-down safety method as the primary approach. In addition to classical safety analysis on single core processors, special attention is required when MCPs are used, as some of the MCP additional features could cause specific failure modes.

#### 2.1 GENERIC SAFETY PROCESS

The avionics safety process is comprised of a descending branch, called allocation, and an ascending branch, called integration [1], as shown in figure 1.

Figure 1. Overview of generic safety process

#### 2.1.1 Top-down Methods for Safe Design Process

"Allocation" pertains to safe design and is performed using top-down analysis methods to design a product complying with the safety constraints. Such safety analysis techniques include the functional hazard assessment (FHA) and the preliminary system safety assessment (PSSA). The FHA identifies and classifies the failure conditions associated with the basic functions of the aircraft according to their severity. The PSSA defines the mitigation, by architecture, of the failure conditions, including the assignment to each function of a development assurance level (DAL) according to the severity of the failure condition.

These methods need to be applied to all hazards, including those specific to MCPs. The outcome is a set of qualitative safety requirements (e.g., defining the safety mechanisms to be implemented) and quantitative safety requirements (e.g., prescribed probability of failure, performance criteria for safety mechanisms).